【导读】近日,奎芯科技自立研发的LPDDR5X PHY IP于8nm工艺上顺遂完成流片验证。实测不仅不变到达9600Mbps速度,更超频跑通10.8Gbps,揭示出于进步前辈工艺节点上挑战极致带宽的特殊能力,为高机能计较、AI边沿计较等场景提供了高性价比的内存接口方案。

满血机能:从尺度到巅峰的超过

2-rank DRAM测试子板挂载方案

本次流片验证采用了挂载2-rank DRAM测试子板的方案,周全笼罩了从低速到极速的事情场景。

满血达标:该IP于1000Mbps至9600Mbps的速度规模内实现了DLL的精准锁定。

极致冲破:于完成8533Mbps及9600Mbps尺度读写测试的基础上,该IP乐成实现了10.8Gbps的超频运行。

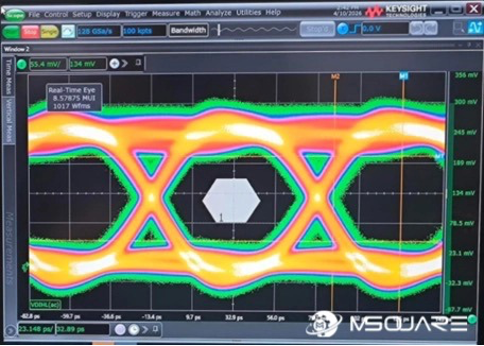

旌旗灯号质量:示波器实测眼图显示(见下图),于10.8Gbps超高带宽下,眼图清楚、裕量足够,PHY IO驱动能力与旌旗灯号完备性优秀。

10.8Gbps速度下实测眼图,眼宽与眼高裕量足够

技能深耕:全栈功效验证经由过程

陈诉指出,该LPDDR5X IP于硬件电路与固件算法层面均到达了商用就绪尺度:

焦点电路稳健:PHY PLL事情正常,输出频率切合寄放器预期读取值;ZQ电阻校准与IO配置均切合设计预期。

软件算法成熟:要害的SW Training环节实现全项经由过程,包括DCC、CBT、Write Leveling以和繁杂的Read/Write DQ 1D/2D Training。这确保了该IP可以或许主动适配差别情况,为客户提供“即插即用”的不变体验。

高负载撑持:乐成经由过程2-rank DRAM挂载测试,证实了其于年夜容量、重负载运用场景下的靠得住性。

上述全栈功效验证的经由过程,象征着该IP已经具有商用就绪能力。对于客户而言,采用奎芯科技的LPDDR5X IP:

于8nm工艺上便可得到原本需更进步前辈制程才能实现的内存带宽;

“硅验证+完备练习算法”年夜幅降低集成危害,缩短芯片上市周期。

奎芯LPDDR5X IP:进步前辈制程下的高机能之选

于高机能计较、智能座舱、边沿AI运用和高端挪动装备范畴,内存带宽及功耗已经成为焦点瓶颈。这次基在知名FAB 8nm工艺的LPDDR5X IP乐成验证,是奎芯科技IP营业为业界带来的又一高机能产物。

将来,奎芯科技将继承致力在为全世界SoC厂商提供更具竞争力的进步前辈毗连方案,助力AI与高机能计较时代的财产进级。